Efficient Large Scale DLRM Implementation on Heterogeneous Memory Systems

Mark Hildebrand, Jason Lowe-Power, Venkatesh Akella High Performance Computing: 38th International Conference, ISC High Performance 2023.

HammerSim: A Tool to Model Rowhammer

Kaustav Goswami, Ayaz Akram, Hari Venugopalan, Jason Lowe-Power, Young Architect Workshop at ASPLOS 2023.

Validating gem5’s Memory Components

Mahyar Samani, Jason Lowe-Power, gem5 workshop at ISCA 2022.

Rethinking the Management Techniques in Emerging Memory Systems

Maryam Babaie, Ayaz Akram, Jason Lowe-Power MICRO 2022: The 8th CWIDCA Workshop.

Toward High-Fidelity Heterogeneous Memory System Modeling in gem5

Maryam Babaie, Ayaz Akram, Jason Lowe-Power ModSim 2022: Workshop on Modeling & Simulation of Systems and Applications

A Cycle-level Unified DRAM Cache Controller Model in gem5

Maryam Babaie, Ayaz Akram, Jason Lowe-Power ISCA 2022: The 4th gem5 Tutorial and User’s Workshop.

SoK: Limitations of Confidential Computing via TEEs for High-Performance Compute Systems

Ayaz Akram, Venkatesh Akella, Sean Peisert, Jason Lowe-Power. IEEE International Symposium on Secure and Private Execution Environment Design (SEED) 2022.

Modeling HBM2 Memory Controller

Ayaz Akram, Maryam Babaie, Wendy Elsasser, Jason Lowe-Power. The 4th gem5 Users’ Workshop associated with ISCA 2022.

LLM: Realizing Low-Latency Memory by Exploiting Embedded Silicon Photonics for Irregular Workloads

Marjan Fariborz, Mahyar Samani, Pouya Fotouhi, Roberto Proietti, Il-min yi, Venkatesh Akella, Jason Lowe-Power, Samuel Palermo, S. J. Ben Yoo ISC-HPC 2022.

HTA: A Scalable High-Throughput Accelerator for Irregular HPC Workloads

Pouya Fotouhi, Marjan Fariborz, Roberto Proietti, Jason Lowe-Power, Venkatesh Akella, S. J. Ben Yoo ISC-HPC 2021.

Enabling Design Space Exploration for RISC-V Secure Compute Environments

Ayaz Akram, Venkatesh Akella, Sean Peisert, Jason Lowe-Power. Fifth Workshop on Computer Architecture Research with RISC-V (CARRV 2021). With ISCA 2021.

Performance Analysis of Scientific Computing Workloads on General Purpose TEEs

Ayaz Akram, Anna Giannakou, Venkatesh Akella, Jason Lowe-Power, Sean Peisert. 35th IEEE International Parallel & Distributed Processing Symposium (IPDPS ...

How to develop a bad research tool

Jason Lowe-Power. 2021 Workshop on Negative results, Opportunities, Perspectives, and Experiences (NOPE 2021). Held with ASPLOS. 2021

A Case Against Hardware Managed DRAM Caches for NVRAM based Systems

Best paper nominee Mark Hildebrand, Julian T. Angeles, Jason Lowe-Power, Venkatesh Akella 2021 IEEE International Symposium on Performance Analysis of System...

Enabling reproducible and agile full-system simulation

Best paper nominee Bobby R. Bruce, Ayaz Akram, Hoa Nguyen, Kyle Roarty, Mahyar Samani, Marjan Fariborz, Trivikram Reddy, Matthew D. Sinclair, Jason Lowe-Powe...

Investigating Hardware Caches for Terabyte-scale NVDIMMs

Julian T. Angeles, Mark Hildebrand, Venkatesh Akella, Jason Lowe-Power 12TH Annual Non-volatile Memories Workshop (NVMW 2021) 2021.

HCAPP: Scalable Power Control for Heterogeneous 2.5D Integrated Systems

Kramer Straube, Jason Lowe-Power, Christopher Nitta, Matthew Farrens, Venkatesh Akella. ICPP 2020.

AutoTM: Automatic Tensor Movement in Heterogeneous Memory Systems using Integer Linear Programming

Mark Hildebrand, Jason Lowe-Power, Venkatesh Akella 25th International Conference on Architectural Support for Programming Languages and Operating Systems (...

Using Trusted Execution Environments on High Performance Computing Platforms

Ayaz Akram and Anna Giannakou, Venkatesh Akella, Jason Lowe-Power, Sean Peisert Open-source Enclaves Workshop (OSEW 2019) 2019.

The Davis In-Order (DINO) CPU: A Teaching-focused RISC-V CPU Design

Jason Lowe-Power and Christopher Nitta Workshop on Computer Architecture Education (WCAE) 2019.

FlexCPU: A Configurable Out-of-Order CPU Abstraction

Bradley Wang, Ayaz Akram, Jason Lowe-Power ISPASS 2019.

Improving Provisioned Power Efficiency in HPC Systems with GPU-CAPP

Kramer Straube, Jason Lowe-Power, Christopher Nitta, Matthew Farrens, and Venkatesh Akella. HiPC 2018.

Integrating Cycle Accurate Chisel Models with gem5’s System Simulation

Nima Ganjehloo, Jason Lowe-Power, Venkatesh Akella. CCC 2018.

A Case for Exposing Extra-Architectural State in the ISA

Jason Lowe-Power, Venkatesh Akella, Matthew K. Farrens, Samuel T. King, and Christopher J. Nitta. HASP Workshop with ISCA 2018.

Filtering Translation Bandwidth with Virtual Caching

Hongil Yoon, Jason Lowe-Power, Gurindar S. Sohi. ASPLOS 2018.

Improving Execution Time of Parallel Programs on Large Scale Chip Multiprocessors with Constant Average Power Processing

Kramer Straube, Christopher Nitta, Raj Amirtharajah, Matthew Farrens, Venkatesh Akella. ICCD 2018.

When to use 3D Die-Stacked Memory for Bandwidth-Constrained Big Data Workloads

Jason Lowe-Power, Mark D. Hill, David A. Wood. BPOE Workshop with ASPLOS 2016.

Border Control: Sandboxing Accelerators

Lena E. Olson, Jason Lowe-Power, Mark D. Hill, David A. Wood MICRO 2015.

Implications of Emerging 3D GPU Architecture on the Scan Primitive

Jason Power, Yinan Li, Mark D. Hill, Jignesh M. Patel, David A. Wood. SIGMOD Record 2015.

Toward GPUs being mainstream in analytic processing: An initial argument using simple scan-aggregate queries

Jason Power, Yinan Li, Mark D. Hill, Jignesh M. Patel, David A. Wood. DaMoN (with SIGMOD) 2015.

gem5-gpu: A Heterogeneous CPU-GPU Simulator

Jason Power, Joel Hestness, Marc S. Orr, Mark D. Hill and David A. Wood. Computer Architecture Letters 2014.

Supporting x86-64 address translation for 100s of GPU lanes

Jason Power, Mark D. Hill,, David A. Wood. HPCA 2014.

Heterogeneous system coherence for integrated CPU-GPU systems

Jason Power, Arkaprava Basu, Junli Gu, Sooraj Puthoor, Bradford M. Beckmann, Mark D. Hill, Steven K. Reinhardt, and David A. Wood MICRO 2013.

- Living reference work

- © 2022

Handbook of Computer Architecture

- Anupam Chattopadhyay ORCID: https://orcid.org/0000-0002-8818-6983 0

Sch of Computer Science & Engineering, Nanyang Technological University, Singapore, Singapore

You can also search for this editor in PubMed Google Scholar

- Reviews exhaustively the basic to the most advanced topics in computer architecture

- Includes in-depth study of design methodologies and tools for computer architectures

- Covers diverse types of architectures, ranging from ASICs, FPGAs to Multicores

5646 Accesses

8 Citations

7 Altmetric

- Table of contents

About this book

Editors and affiliations, about the editor, bibliographic information.

- Publish with us

This is a preview of subscription content, log in via an institution to check for access.

Table of contents (33 entries)

Accelerator design with high-level synthesis.

- Christian Pilato, Stephanie Soldavini

Approximate Computing Architectures

- Muhammad Abdullah Hanif, Vojtech Mrazek, Muhammad Shafique

Architecture Description Languages

- Anupam Chattopadhyay, Zheng Wang, Grant Martin

Architectures for Machine Learning

- Yongkui Yang, Chao Chen, Zheng Wang

Architectures for Multimedia Processing: A Cross-Layer Perspective

- Muhammad Shafique, Bharath Srinivas Prabakaran

Architectures for Quantum Information Processing

- Suryansh Upadhyay, Mahabubul Alam, Swaroop Ghosh

Architectures for Self-Powered Edge Intelligence

- Amit Ranjan Trivedi, Jaeha Kung, Jong Hwan Ko

Bit-Level Model Checking

- Alexander Ivrii, Yakir Vizel

Coarse-Grained Reconfigurable Array (CGRA)

- Zhaoying Li, Dhananjaya Wijerathne, Tulika Mitra

Compute-in-Memory Architecture

- Hongwu Jiang, Shanshi Huang, Shimeng Yu

Dataflow Models of Computation for Programming Heterogeneous Multicores

- Jeronimo Castrillon, Karol Desnos, Andrés Goens, Christian Menard

Design and Tool Solutions for Monolithic Three-Dimensional Integrated Circuits

- Kyungwook Chang, Sung Kyu Lim

Design Automation Techniques for Microfluidic Biochips

- Xing Huang, Tung-Che Liang, Zhanwei Zhong, Tsung-Yi Ho, Krishnendu Chakrabarty

Fault Tolerant Architectures

- Siva Satyendra Sahoo, Anup Das, Akash Kumar

Field-Programmable Gate Array Architecture

- Andrew Boutros, Vaughn Betz

FPGA-Specific Compilers

- Nitish Srivastava, Gai Liu, Yi-Hsiang Lai, Zhiru Zhang

GPU Architecture

- Hyeran Jeon

High-Level Formal Equivalence

- Theo Drane, M. V. Achutha Kiran Kumar

Information Flow Verification

- Cynthia Sturton, Ryan Kastner

Methodologies for Design Space Exploration

- Andy D. Pimentel

- Single Core Processors

- Multicore Processors

- Application-Specific Processors

- Reconfigurable Architectures

- 3D Architectures

- Processor Design Flows

- Processor Programming Flows

- Security Verification

- Neuromorphic Computing

- Quantum Computing

Sch of Computer Science & Engineering, Nanyang Technological University, Singapore, Singapore

Anupam Chattopadhyay

Sayak Ray , Intel, San Jose, California, USA

Book Title : Handbook of Computer Architecture

Editors : Anupam Chattopadhyay

DOI : https://doi.org/10.1007/978-981-15-6401-7

Publisher : Springer Singapore

eBook Packages : Springer Reference Engineering , Reference Module Computer Science and Engineering

eBook ISBN : 978-981-15-6401-7 Due: 19 May 2024

Number of Illustrations : 10 b/w illustrations, 10 illustrations in colour

Topics : Circuits and Systems , Processor Architectures , Electrical Engineering , Applications of Mathematics

Policies and ethics

- Find a journal

- Track your research

Computer Science & Engineering

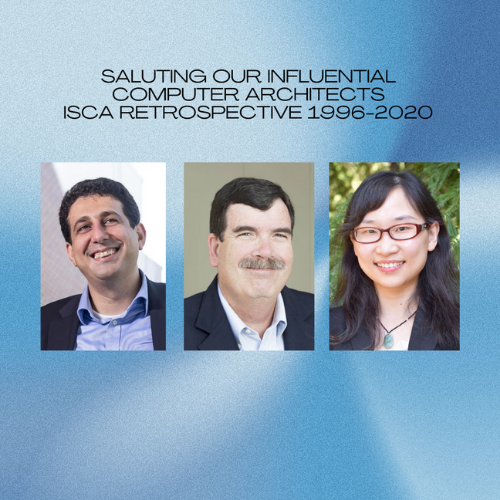

Nine CSE Research Papers in Computer Architecture Included in ISCA’s 25-Year Retrospective

By Kimberley Clementi

In commemoration of its 50th anniversary, the International Symposium on Computer Architecture (ISCA) has compiled a volume of memorable papers – a 25-Year Retrospective: 1996-2020 – to demonstrate the progression of research within computer architecture. The compilation of 98 research papers, culled from a pool of over a thousand submissions, included nine papers from UC San Diego’s Department of Computer Science and Engineering (CSE).

That means CSE faculty were involved in 10 percent of the selected papers.

Hadi Esmaeilzadeh had four research papers included in ISCA’s retrospective, as did CSE Professor Dean Tullsen. Jishen Zhao, an associate professor in the department, had one paper selected.

For more than two decades, their collective research has impacted the trajectory of computer architecture – spanning ground-breaking discoveries related to dark silicon, processors, simultaneous multithreading, and memory systems, enabling applications in machine learning, virtual reality, augmented reality, and artificial intelligence.

Papers for ISCA’s second commemorative volume were chosen by a team of referees to reflect the exciting evolution of computer architecture and share areas of potential growth. ISCA’s first volume, its 25 th anniversary retrospective, was published in 1998.

CSE faculty research included in ISCA@50 25-Year Retrospective: 1996-2020 :

Hadi Esmaeilzadeh – Bridging Computer Architecture and New Applications

Esmaeilzadeh, the inaugural holder of the Halıcıoğlu Chair in Computer Architecture at UC San Diego, is building the computer architecture that will enable AI and ML technologies of the future. He and his colleagues have focused on bridging the gap between the microarchitecture of processors and the increasing levels of performance required by computation-hungry applications. His highly-cited 2011 paper outlined this dilemma, while his more recent research proposes an architectural framework – dubbed Bit Fusion – developed to preserve accuracy while enabling ultra-power efficiency for deep learning.

Dark silicon and the end of multicore scaling

A reconfigurable fabric for accelerating large-scale datacenter services

General-purpose code acceleration with limited-precision analog computation

Bit Fusion: Bit-Level Dynamically Composable Architecture for Accelerating Deep Neural Network

Dean Tullsen – Standing the Test of Time

Widely considered one of computer architecture’s most influential researchers, CSE Professor Dean Tullsen has amassed five Test of Time Awards. This includes one for novel research on heterogenous multi-core architectures , which led to the design of many modern processors such as Qualcomm’s Snapdragon and Apple’s M1Pro and M1Max. Tullsen’s earlier contributions – including the introduction of simultaneous multithreading – were also deeply grounded in the issues of real, industry-leading processor design.

Exploiting choice: instruction fetch and issue on an implementable simultaneous multithreading processor

Selective value prediction

Single-ISA Heterogeneous Multi-Core Architectures for Multithreaded Workload Performance

Interconnections in Multi-Core Architectures: Understanding Mechanisms, Overheads and Scaling

Jishen Zhao – Creating Memorable Work in PIM

Zhao’s research stretches the boundary between computer architecture and system software, particularly in memory systems. Her 2016 ISCA paper showcases the possibilities that arise from combining emerging applications such as AI with technologies like ReRam, playing a crucial role in advancing research in Processing-in-Memory (PIM).

PRIME: a novel processing-in-memory architecture for neural network computation in ReRAM-based main memory

- Who’s Teaching What

- Subject Updates

- MEng program

- Opportunities

- Minor in Computer Science

- Resources for Current Students

- Program objectives and accreditation

- Graduate program requirements

- Admission process

- Degree programs

- Graduate research

- EECS Graduate Funding

- Resources for current students

- Student profiles

- Instructors

- DEI data and documents

- Recruitment and outreach

- Community and resources

- Get involved / self-education

- Rising Stars in EECS

- Graduate Application Assistance Program (GAAP)

- MIT Summer Research Program (MSRP)

- Sloan-MIT University Center for Exemplary Mentoring (UCEM)

- Electrical Engineering

- Computer Science

- Artificial Intelligence + Decision-making

- AI and Society

- AI for Healthcare and Life Sciences

- Artificial Intelligence and Machine Learning

- Biological and Medical Devices and Systems

- Communications Systems

- Computational Biology

- Computational Fabrication and Manufacturing

- Computer Architecture

- Educational Technology

- Electronic, Magnetic, Optical and Quantum Materials and Devices

- Graphics and Vision

- Human-Computer Interaction

- Information Science and Systems

- Integrated Circuits and Systems

- Nanoscale Materials, Devices, and Systems

- Natural Language and Speech Processing

- Optics + Photonics

- Optimization and Game Theory

- Programming Languages and Software Engineering

- Quantum Computing, Communication, and Sensing

- Security and Cryptography

- Signal Processing

- Systems and Networking

- Systems Theory, Control, and Autonomy

- Theory of Computation

- Departmental History

- Departmental Organization

- Visiting Committee

- Explore all research areas

We design the next generation of computer systems. Working at the intersection of hardware and software, our research studies how to best implement computation in the physical world. We design processors that are faster, more efficient, easier to program, and secure. Our research covers systems of all scales, from tiny Internet-of-Things devices with ultra-low-power consumption to high-performance servers and datacenters that power planet-scale online services. We design both general-purpose processors and accelerators that are specialized to particular application domains, like machine learning and storage. We also design Electronic Design Automation (EDA) tools to facilitate the development of such systems.

Advances in computer architecture create quantum leaps in the capabilities of computers, enabling new applications and driving the creation of entirely new classes of computer systems. For example, deep learning, which has transformed many areas of computer science, was made practical by hardware accelerators (initially GPUs and later more specialized designs); and advances in computer performance have also made self-driving cars and autonomous drones possible.

Computer architecture spans many layers of the hardware and software stack, and as a result we collaborate with researchers in many other areas. For example, several of our current projects focus on the design of domain-specific architectures, and involve researchers in programming languages and compilers to ensure that our systems are broadly useful, as well as domain experts. In addition, the waning of Moore’s Law is making emerging technologies, like CN-FETs, photonics, or resistive memories, an attractive way to implement computation, sparking collaborations with experts in these areas.

Latest news in computer architecture

Department of eecs announces 2024 promotions.

The Department of Electrical Engineering and Computer Science (EECS) is proud to announce multiple promotions.

EECS Alliance Roundup: 2023

Founded in 2019, The EECS Alliance program connects industry leading companies with EECS students for internships, post graduate employment, networking, and collaborations. In 2023, it has grown to include over 30 organizations that have either joined the Alliance or participate in its flagship program, 6A.

2023-24 EECS Faculty Award Roundup

This ongoing listing of awards and recognitions won by our faculty is added to all year, beginning in September.

Department of EECS announces 2023 promotions

The department is proud to announce multiple promotions this year.

Recent chair announcements within EECS

The Department of Electrical Engineering and Computer Science (EECS) recently announced the following crop of chair appointments, all effective July 1, 2022. Karl Berggren has been named the …

Upcoming events

Doctoral thesis: nonparametric high-dimensional models: sparsity, efficiency, interpretability, eecs inspiration series: spreeai ceo, doctoral thesis: designing a learner-centric future for skill-learning, doctoral thesis: machine learning for sepsis prognosis: prediction models and dissecting electronic health records, doctoral thesis: machine learning approaches for healthcare discovery, delivery, and equity, doctoral thesis: efficient deep learning with sparsity: algorithms, systems, and applications.

A new direction for computer architecture research

Ieee account.

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

IMAGES

VIDEO

COMMENTS

Communications Preferences. Profession and Education. Technical Interests. Need Help? US & Canada:+1 800 678 4333. Worldwide: +1 732 981 0060. Contact & Support. About IEEE Xplore. Contact Us.

Heterogeneous system coherence for integrated CPU-GPU systems. Jason Power, Arkaprava Basu, Junli Gu, Sooraj Puthoor, Bradford M. Beckmann, Mark D. Hill, Steven K. Reinhardt, and David A. Wood MICRO 2013. Computer Architecture Research Group at UC Davis ECE/CS.

In computer science and engineering, computer architecture is the practical art of defining the structure and relationship of the subcomponents of... | Explore the latest full-text research PDFs ...

applications. Indeed, the computer architecture research community has recognized and embraced specialization: of 175 papers in the 2016 computer architecture conferences (ISCA, HPCA, MICRO), 38 papers address specialization with GPUs or application-specific accelerators, while another 17 address specialized designs for machine learning.

Fowers, J. et al. A configurable cloud-scale DNN processor for real-time AI. In Proceedings of the 45<sup>th</sup> ACM/IEEE Annual International Symposium on Computer Architecture (Los Angeles, CA, June 2--6). IEEE, 2018, 1--14. Google Scholar Digital Library; Hennessy, J. and Patterson, D. A New Golden Age for Computer Architecture.

This annual publication presents 12 articles selected from major computer architecture conferences of the year. The 12 papers are recognized for their importance, mainly the long-term impact and influence on the industry and other researchers. The selection committee members put enormous effort into picking the papers. We asked what the criteria should be for the top picks, and then we tried ...

Adopted extensively in computer architecture research and engineering, cycle-accurate discrete-event simulators (DES) enable new architectural ideas, as well as design space exploration. DES is ... This paper aims to explore the possibility of an ML-based computer architecture simulation approach given the following reasons. First, ML models ...

Arch2030: A Vision of Computer Architecture Research over the Next 15 Years. Luis Ceze, Mark D. Hill, Thomas F. Wenisch. Application trends, device technologies and the architecture of systems drive progress in information technologies. However, the former engines of such progress - Moore's Law and Dennard Scaling - are rapidly reaching the ...

Vector IRAM (VIRAM) [24], the architecture proposed by the research group of the authors, is a first effort for a processor architecture and design that matches the requirements of the mobile personal environment. VIRAM is based on two main ideas, vector processing and the integrationof logic and DRAM on a single chip.

This handbook presents the key topics in the area of computer architecture covering from the basic to the most advanced topics, including software and hardware design methodologies. It will provide readers with the most comprehensive updated reference information covering applications in single core processors, multicore processors, application ...

The author introduces the top picks selection of papers in computer architecture that were published in 2018. This is the 16th year of publication of what has now become a tradition in the computer architecture community. Each year, the MICRO Top Picks selection committee, which I chaired for this year, selects 12 papers for this special issue, to highlight for the IEEE Micro readership, a ...

computer architecture. The research paper focuses on . the question of which is the following computer . architecture is more suited for serves and in which . Volume 7, Issue 3, ...

In commemoration of its 50th anniversary, the International Symposium on Computer Architecture (ISCA) has compiled a volume of memorable papers - a 25-Year Retrospective: 1996-2020 - to demonstrate the progression of research within computer architecture. The compilation of 98 research papers, culled from a pool of over a thousand ...

Journal of Computer Science Original Research Paper Conceptual Modeling for Computer Organization and Architecture Sabah Al-Fedaghi Department of Computer Engineering, Kuwait University, Kuwait City, Kuwait Article history Received: 10-01-2021 Revised: 18-02-2021 Accepted: 18-02-2021 Email: [email protected]

Summary form only given. This panel focuses on the industrial vision for the future of computer architecture research. The field of computer architecture is in critical need for focus, perhaps now more than ever. The underlying technology is presenting significant roadblocks for next generation designs. The applications that the world wants seem to be out of synch with mainstream research. The ...

The ev ent was held in conjunction. with the 31st International Symposium on Computer Architecture and High Performance Computing, SBAC-P AD 2019, in Campo Grande, MS, Brazil, from October 15 to ...

Current computer architecture research continues to have a bias for the past in that it focuses on desktop and server applications. In our view, a different computing domain— personal mobile computing —will play a significant role in driving technology in the next decade. This domain will pose a different set of requirements

In this paper we suggest a different computing environment as a worthy new direction for computer architecture research: personal mobile computing, where portable devices are used for visual computing and personal communications tasks. ... We do not believe that VIRAM is the last word on computer architecture research for mobile multimedia ...

Computer Architecture. We design the next generation of computer systems. Working at the intersection of hardware and software, our research studies how to best implement computation in the physical world. We design processors that are faster, more efficient, easier to program, and secure. Our research covers systems of all scales, from tiny ...

Abstract: Every year, IEEE Micro publishes a special issue that recognizes the most significant research outcomes in computer architecture in terms of novelty and potential for long-term impact. Continuing this tradition, the 2022 selection committee identified 12 articles as top picks from the 2022 computer architecture conferences and another 12 articles as honorable mentions.

In this paper, we present a comprehensive review of the work that applies ML for computer architecture and system design. First, we perform a high-level taxonomy by considering the typical role that ML techniques take in architecture/system design, i.e., either for fast predictive modeling or as the design methodology.

In the past few years, two important trends have evolved that could change the shape of computing: multimedia applications and portable electronics. Together, these trends will lead to a personal mobile-computing environment, a small device carried all the time that incorporates the functions of the pager, cellular phone, laptop computer, PDA, digital camera, and video game. The microprocessor ...

e-mail: [email protected]. Abstract —Traditional computer architecture consists of six. parts: controller, arithmetic unit, m emory, storage, input and. output. Th e memory access speed is fast ...

arXiv.org e-Print archive